# A Hardware/Software Co-Design Approach for Ethernet Controllers to Support Time-triggered Traffic in the Upcoming IEEE TSN Standards

Friedrich Groß Till Steinbach

Franz Korf Thomas C. Schmidt Bernd Schwarz

Hamburg University of Applied Sciences {friedrich.gross, till.steinbach, korf, schmidt, schwarz}@informatik.haw-hamburg.de

4th IEEE International Conference on Consumer Electronics - Berlin September 8th, 2014

# **Agenda**

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

- 1 Introduction & Motivation

- 2 Concept & Results

- 3 Conclusion & Outlook

#### Motivation

Why is Time-Triggered Ethernet needed?

- Modern cars: > 70 ECUs; about 2500 message types

- Bandwidth and timing requirements increase

- Now used communication systems came to their limits due they are not scalable

- Next generation backbones will most likely base on real-time Ethernet

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

## Introduction

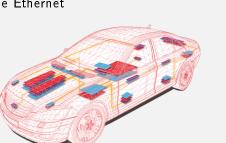

#### How TDMA in Time-Triggered Ethernet works

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

#### Introduction

#### Properties of Time-Triggered Ethernet

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

- Real-time extension for standard Ethernet

- Deterministic behavior, low latency and jitter

- Clock synchronisation and special switches are needed

- TTEthernet, Profinet IRT, upcoming IEEE 802.1Qbv, ...

- This work focuses TTEthernet AS6802

Introduction & Motivation

Concept & Results

#### Motivation

Why Hardware/Software Co-Design?

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

Conclusion & Outlook

- Reduce computational power

- On a high network load up to 90% of a CPU is used (ARM9 @ 200Mhz) <sup>1</sup>

- One reception buffer for all traffic-classes

- Every received frame must be handled immediately for garbage collection

- Reduce timing requirements for OS

- CAN-Bus and FlexRay achieved good results with HW/SW Co-Design

<sup>1</sup>K. Müller "A Real-time Ethernet Prototype Platform for Automotive Applications," in 2011 ICCE-Berlin

## Contribution

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

- Scalable HW/SW Co-Design TTEthernet Controller

- Include clock synchronisation

- Results of a prototype implementation on a FPGA

# **Agenda**

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

Conclusion & Outlook

1 Introduction & Motivation

2 Concept & Results

# **Concept**Typical Ethernet Design

CPU CPU-Bus 1-to-1 **FIFO** MAC External Memory RAM controller PHY HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

## Concept Main Idea

CPU CPU-Bus 1-to-1 Time-MAC Triggered **Ethernet** Coprocessor PHY

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

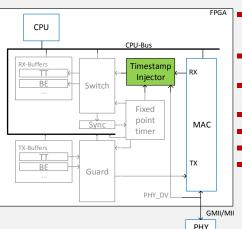

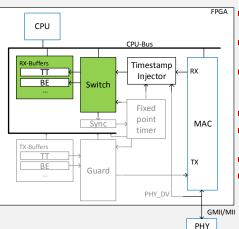

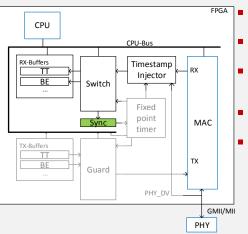

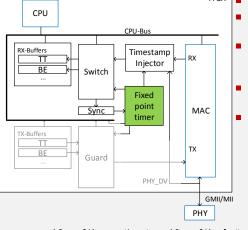

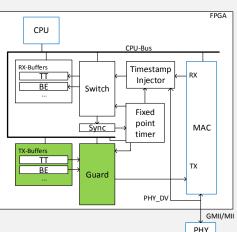

FPGA CPU CPU-Bus RX-Buffers Timestamp RX Injector BE Switch Fixed MAC timer TX-Buffers ΤX Guard PHY DV GMII/MII PHY

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

#### Architecture - Timestamp Injector

- Timestamps needed for Synchronisation and validation of TT Frames

- SW-Implementation has low accuracy

- Record Timestamps with PHY\_DV (10 ns jitter)

- Validate with rx interrupt

- FIFO for TS

- Works on the fly

- Delay of 2 clock cycles

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

Conclusion & Outlook

109 LUTs ( $\widehat{=}$  5%); 72 Flip Flops ( $\widehat{=}$  3.8%) of all (+ HW FIFO)

# Concept Architecture - Switch

- Need to separate Traffic to different Buffers

- SW-Implementation needs the most CPU-Resources

- Switches based on Dest-MAC, Ether-Type, Timestamp

- Independent interrupts

- Application specific buffer size

- Works on the fly

- Delay of 6 clock cycles

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

Conclusion & Outlook

307 LUTs ( $\widehat{=}$  14.1%); 529 Flip Flops ( $\widehat{=}$  11.7%) of all

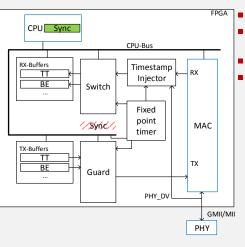

#### Architecture - Synchronisation

- Synchronize internal clock to network clock

- SW-Implementation need more energy

- On full HW-Implementation OS modification is very low

- Full AS6802 client implement ation

- Rate-correction

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction &

Concept & Results

Conclusion & Outlook

1100 LUTs (≘ 50.3%); 736 Flip Flops (≘ 21%) of all

#### Architecture - Fixed point timer

- Addon for Synchronisation

- Keeps clock synchronized during the whole cycle

- Smaller reservation window

- -> more bandwidth

- SW-Implementation impossible

- Rate-correctable timer implemented as Fixed-Point timer

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction &

Concept & Results

Conclusion & Outlook

55 LUTs ( $\hat{=}$  2.5%); 55 Flip Flops ( $\hat{=}$  1.2%) of all

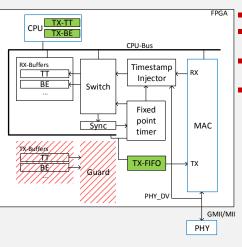

#### Architecture - TX-Buffers and Guard

Sends TT on schedule and BE messages between TT messages

- CPU can put async messages to Buffers

- OS don't need

Time-Triggered schedule functions

- SW-Implementation has high Jitter 1µs to 10µs

- HW-Implementation has 80ns Jitter

- Application specific buffer size

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

Conclusion & Outlook

614 LUTs ( $\widehat{=}$  28.1%); 475 Flip Flops ( $\widehat{=}$  5.4%) of all

# **Concept**Possible Partitioning

- CPU-Res.: few percent

- HW-Res.: safe 21% FF's and 50.3% LUT's

- Accuracy: no effect

- Energy: much higher

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction &

Concept & Results

# **Concept**Possible Partitioning

- CPU-Res.: few percent

- HW-Res.: safes 1% FIFO's and 18.6% LUT's

- Accuracy: Jitter rises up to 10µs

- Energy: still is no statement possible

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

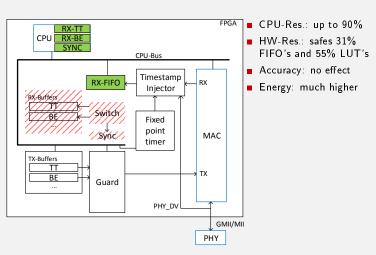

# Concept HW/SW Co-Design

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

# **Agenda**

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

- 1 Introduction & Motivation

- 2 Concept & Results

- 3 Conclusion & Outlook

## **Conclusion**

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

- Full Hardware implementation of a TTEthernet Controller

- Approach how to scale it

- Result: HW/SW Co-Design is a good way to deduce CPU consumption of a Time-Triggered Ethernet protocol stack.

## Outlook

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction & Motivation

Concept & Results

- AUTOSAR is a automotive system architecture without time-triggered scheduling mechanisms

- Develop driver for AUTOSAR

- Run different partitions of HW/SW Co-Desing

# Thank you!

HW/SW Co-Design for TDMA Ethernet controllers

F. Groß

Introduction &

Concept & Results

Conclusion & Outlook

Thank you for your attention!

■ Website of CoRE research group: http://www.haw-hamburg.de/core

SPONSORED BY THE